Government of Nepal Ministry of Education, Science and Technology Curriculum Development Centre Sanothimi, Bhaktapur Phone : 5639122/6634373/6635046/6630088 Website : www.moecdc.gov.np

# **Computer Engineering**

10

# Microprocessor

Technical and Vocational Stream Learning Resource Material

## Microprocessor (Grade 10)

# Secondary Level Computer Engineering

Government of Nepal Ministry of Education, Science and Technology **Curriculum Development Centre** Sanothimi, Bhaktapur

#### Publisher: Government of Nepal

Ministry of Education, Science and Technology

#### **Curriculum Development Centre**

Sanothimi, Bhaktapur

© Publisher

Layout by Khados Sunuwar

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted, in any other form or by any means for commercial purpose without the prior permission in writing of Curriculum Development Centre.

### Preface

The curriculum and curricular materials have been developed and revised on a regular basis with the aim of making education objective-oriented, practical, relevant and job oriented. It is necessary to instill the feelings of nationalism, national integrity and democratic spirit in students and equip them with morality, discipline and self-reliance, creativity and thoughtfulness. It is essential to develop in them the linguistic and mathematical skills, knowledge of science, information and communication technology, environment, health and population and life skills. it is also necessary to bring in them the feeling of preserving and promoting arts and aesthetics, humanistic norms, values and ideals. It has become the need of the present time to make them aware of respect for ethnicity, gender, disabilities, languages, religions, cultures, regional diversity, human rights and social values so as to make them capable of playing the role of responsible citizens with applied technical and vocational knowledge and skills. This Learning Resource Material for Computer Engineering has been developed in line with the Secondary Level Computer Engineering Curriculum with an aim to facilitate the students in their study and learning on the subject by incorporating the recommendations and feedback obtained from various schools, workshops and seminars, interaction programs attended by teachers, students and parents.

In bringing out the learning resource material in this form, the contribution of the Director General of CDC Dr. Lekhnath Poudel, Pro, Dr. Subarna Shakya, Bibha Sthapit, Kumar Prasun, Yogesh Parajuli, Dr. Romakanta Pandey, Dinesh Khatri, Udayaraj Karki, Rajendra Rokaya is highly acknowledged. The book is written by Sankar Kumar Yadav and the subject matter of the book was edited by Badrinath Timalsina and Khilanath Dhamala. CDC extends sincere thanks to all those who have contributed in developing this book in this form.

This book is a supplimentary learning resource material for students and teachrs. In addition they have to make use of other relevnt materials to ensure all the learning outcomes set in the curriculum. The teachers, students and all other stakeholders are expected to make constructive comments and suggestions to make it a more useful learning resource material.

2076 BS

Ministry of Education, Science and Technology Curriculum Development Centre

| Unit | 1: INTRODUCTION                                                      | 1     |

|------|----------------------------------------------------------------------|-------|

| 1.1  | Definition of Microprocessor and its applications                    | 1     |

| 1.2  | Evolution of Microprocessors                                         | 2     |

| 1.3  | Von Neumann Architecture or IAS (Immediate Access Store)             | 5     |

| 1.4  | Basic Organization of Microprocessors                                | 6     |

| 1.5  | Types of Microprocessor                                              | 10    |

| Unit | 2: Components of Microprocessor                                      | 12    |

| 2.1  | I/O (Input/Output)                                                   | 12    |

| 2.2  | Memory                                                               | 12    |

|      | 2.2.1 Primary Memory                                                 | 12    |

|      | 2.2.2 Secondary Memory                                               | 12    |

|      | 2.2.3 Cache Memory                                                   | 13    |

| 2.3  | PROCESSOR UNIT                                                       | 13    |

| 2.4  | Bus Structure of 8085                                                | 14    |

| Unit | 3: Instruction Cycle                                                 | 16    |

| 3.1  | Instruction cycle, Machine cycle & T-states                          | 16    |

| 3.2  | Machine cycle of 8085 microprocessor                                 | 16    |

|      | 3.2.1 Opcode Fetch Machine Cycle                                     | 17    |

|      | 3.2.2 Memory Read Machine Cycle                                      | 17    |

|      | 3.2.3 Memory Write Machine Cycle                                     | 17    |

|      | 3.2.4 I/O Read Machine Cycle                                         | 17    |

|      | 3.2.5 I/O Write Machine Cycle                                        | 17    |

| 3.3  | Timing Diagram                                                       | 17    |

| Unit | 4: Intel 8085 Microprocessor                                         | 23    |

| 4.1  | Fnctional Block Diagram                                              | 23    |

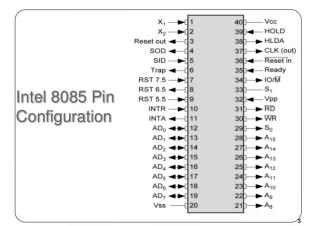

| 4.2  | Pin Configuration Of 8085                                            | 23    |

| 4.3  | Description of each blocks: Registers, Flag, Data and Address Bus, T | iming |

|      | and Control Unit, Interrupts                                         | 24    |

| 4.4. | Instructions- Opcode and Operands                                    | 28    |

| 4.5  | Addressing Modes in 8085                                             | 29    |

| Unit | 5: Programming with Intel 8085 Microprocessor                        | 31 |

|------|----------------------------------------------------------------------|----|

| 5.1  | Instruction format and data format                                   | 31 |

| 5.2  | Intel 8085 instruction Set& Instructions types                       | 33 |

| 5.3  | Assembly language program and flowchart                              | 37 |

| Unit | 6: Basic I/O, Memory R/W and Interrupt Operations                    | 45 |

| 6.1  | Memory Read Operation:                                               | 45 |

| 6.2  | Direct Memory Access (DMA)                                           | 46 |

| 6.3  | Interrrupts                                                          | 48 |

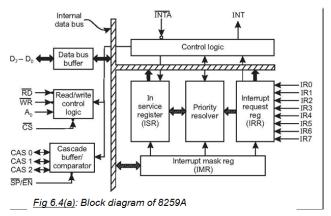

| 6.4  | 8259 Operations                                                      | 51 |

| Unit | 7 : Input/Output Interfaces                                          | 55 |

| 7.1  | Parallel Communication: Introduction & Applications                  | 55 |

| 7.2  | Serial Communication                                                 | 56 |

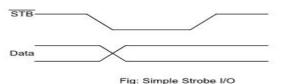

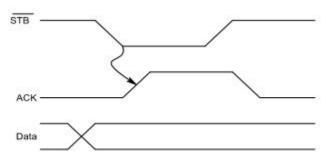

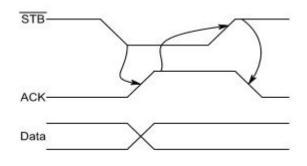

| 7.3  | Simple I/O, Strobe I/O, Single handshake I/O, Double handshake I/O59 |    |

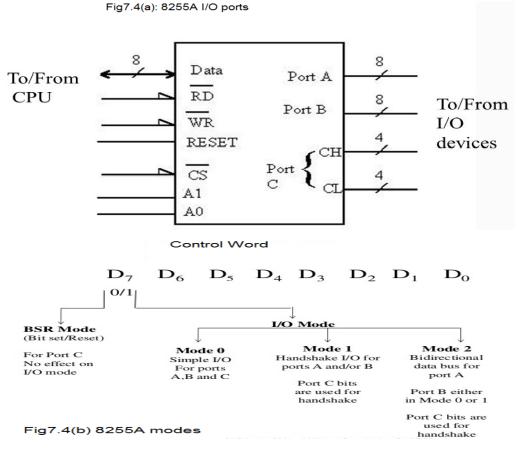

| 7.4  | 8255A (PPI) and its working principal                                | 61 |

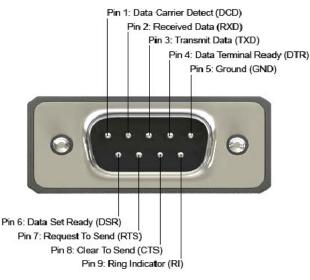

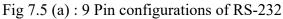

| 7.5. | RS-232: Introduction, pin configuration (9 pin and 25 pin)           | 66 |

### Unit: 1

### INTRODUCTION

### 1.1 Definition of Microprocessor and its applications

Microprocessor is basically a programmable IC. A microprocessor is a computer processor which incorporates the functions of a computer's central processing unit (CPU) on a single integrated circuit (IC) or at most a few integrated circuits. The microprocessor is a multipurpose, clock driven, register based, digital-integrated circuit which accepts binary data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors contain both combinational logic and sequential digital logic. Microprocessors operate on numbers and symbols represented in the binary number system.

### **Applications of Microprocessor**

Microprocessor is a mass storage device. They are the advanced form of computers. They are also called as microcomputers. The impact of microprocessor in different fields is significant. The availability of low cost, low power and small weight, computing capability makes it useful in different applications. Now-a-day, a microprocessor based systems are used in instructions, automatic testing product, speed control of motors, traffic light control, light control of furnaces etc. Some of the important areas are mentioned below:

### Instrumentation

It is very useful in the field of instrumentation. Frequency counters, function generators, frequency synthesizers, spectrum analyses and many other instruments are available, when microprocessors are used as controller. It is also used in medical instrumentation.

#### Control

Microprocessor based controllers are available in home appliances, such as microwave oven, washing machine etc., microprocessors are being used in controlling various parameters like speed, pressure, temperature etc. These are used with the help of suitable transduction.

### Communication

Microprocessors are being used in a wide range of communication equipment's. In telephone industry, these are used in digital telephone sets. Telephone exchanges and modem etc. The use of microprocessor in television, satellite communication has made teleconferencing possible. Railway reservation and air reservation system also uses this technology. LAN and WAN for communication of vertical information through computer network.

### **Office Automation and Publication**

Microprocessor based microcomputer with software packages has changed the office environment. Microprocessors based systems are being used for word processing, spread sheet operations, storage etc. The microprocessor has revolutionized the publication technology.

### Consumer

The use of microprocessor in toys, entertainment equipment and home applications are making them more entertaining and full of features. The use of microprocessors is more widespread and popular. Now the Microprocessors are used in the following areas/equipments;

- 1. Calculators

- 2. Accounting system

- 3. Game machines

- 4. Complex Industrial Controller

- 5. Traffic light control

- 6. Data acquisition systems

- 7. Military applications.

- 8. Communications systems

- 9. Robotics

### **1.2 Evolution of Microprocessors**

The **Intel 4004** is a 4-bit central processing unit (CPU) released by Intel Corporation in 1971. It was the first commercially available microprocessor. It began as the "Busicom Project", a joint development by America's Intel and

Japan's Busicom with initial design concepts by Busicom's Masatoshi Shima and Sharp's Tadashi Sasaki in 1968, before being designed by Intel's Marcian Ted Hoff and Federico Faggin and Busicom'sShima from 1969 to April 1970. it was completed under Faggin's leadership, with Shima's assistance, in January 1971. It was integrated with 2300 transistors with a max CPU clock rate 740KHZ. We can see details of more microprocessors in following table:

| Name          | Year | Transistors | Data Width | Clock Speed |

|---------------|------|-------------|------------|-------------|

| Intel 4004    | 1971 | 2300        | 4 bits     | 740 KHZ     |

| Intel 4040    | 1974 | 3000        | 4          | 500-740 KHZ |

| Intel 8008    | 1972 | 3300        | 8          | 0.2-0.8 MHZ |

| Intel 8080    | 1974 | 6000        | 8          | 2 MHZ       |

| Intel 8085    | 1976 | 6500        | 8          | 5 MHZ       |

| Intel 8086    | 1978 | 29000       | 16         | 5 MHZ       |

| Intel 8088    | 1979 | 29000       | 8          | 5 MHZ       |

| Intel 80286   | 1982 | 134,000     | 16         | 6 MHZ       |

| 80386         | 1985 | 275,000     | 32         | 16 MHZ      |

| 80486         | 1989 | 1,200,000   | 32         | 25 MHZ      |

| Pentium       | 1993 | 3,100,000   | 32/64 bits | 60 MHZ      |

| Pentium II    | 1997 | 7,500,000   | 64         | 233 MHZ     |

| Pentium III   | 1999 | 9,500,000   | 64         | 450 MHZ     |

| Pentium IV    | 2000 | 42,000,000  | 64         | 1.5 GHZ     |

| Intel Itanium | 2001 | 25,000,000  | 64         | 2 GHZ       |

Table: 1.1

Fig1.1: 16-pin Intel 4004 first microprocessor

Microprocessors were categorized into five generations: first, second, third, fourth, and fifth generations. Their characteristics are described below:

### **First-generation**

The microprocessors that were introduced in 1971 to 1972 were referred to as the

first-generation system. First-generation microprocessors processed their instructions serially—they fetched the instruction, decoded it, then executed it. When an instruction was completed, the microprocessor updated the instruction pointer and fetched the next instruction, performing this sequential drill for each instruction in turn.

#### Second generation

By the late 1970s, enough transistors were available on the IC to usher in the second generation of microprocessor sophistication:16-bit arithmetic and pipelined instruction processing.

Motorola's MC68000 microprocessor, introduced in 1979, is an example. Another example is Intel's 8080. This generation is defined by overlapped fetch, decode, and execute steps (Computer 1996). As the first instruction is processed in the execution unit, the second instruction is decoded and the third instruction is fetched.

The distinction between the first and second-generation devices was primarily the use of newer semiconductor technology to fabricate the chips. This new technology resulted in a five-fold increase in instruction, execution, speed, and higher chip densities.

### Third generation

The third generation, introduced in 1978, was represented by Intel's 8086 and the Zilog-Z8000, which were 16-bit processors with minicomputer-like performance. The third generation came about as IC transistor counts approached 250,000. Motorola's MC68020, for example, incorporated an on-chip cache for the first time and the depth of the pipeline increased to five or more stages. This generation of microprocessors was different from the previous ones in that all major workstation manufacturers began developing their own RISC-based microprocessor architectures (Computer, 1996).

### Fourth generation

As the workstation companies converted from commercial microprocessors to inhouse designs, microprocessors entered their fourth generation with designs surpassing a million transistors. Leading-edge microprocessors such as Intel's 80960CA and Motorola's 88100 could issue and retire more than one instruction per clock cycle.

### Fifth generation

Microprocessors in their fifth generation, employed decoupled super scalar processing, and their design soon surpassed 10 million transistors. In this generation, PCs are a low-margin, high-volume-business dominated by a single microprocessor.

### 1.3 Von Neumann Architecture or IAS (Immediate Access Store)

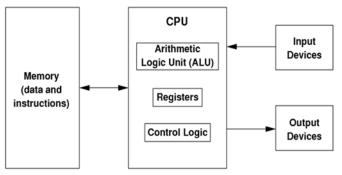

A Von Neumann Architecture machine, designed by physicist and mathematician John von Neumann (1903–1957) is a theoretical design for a stored program computer that serves as the basis for almost all modern computers. A Von Neumann Machine consists of a central processor with an arithmetic/logic unit and a control unit, a memory, mass storage, and input and output.

The von Neumann machine was created by its namesake, John Von Neumann, a physicist and mathematician, in 1945, building on the work of Alan Turing. The design was published in a document called "First Draft of a Report on the EDVAC."

The report described the first stored-program computer. Earlier computers, such as the ENIAC, were hard-wired to do one task. If the computer had to perform a different task, it had to be rewired, which was a tedious process. With a stored-program computer, ageneral purpose computer could be built to run different programs.

The theoretical design consists of:

- A central processor consisting of a control unit and an arithmetic/logic unit

- A memory unit

- Input and output unit

The Von Neumann Design thus forms the basis of modern computing. A similar model, the Harvard architecture, had dedicated data address and buses for both reading and writing to memory. The von Neumann Architecture won out because it was simpler to implement in real hardware.

Figure 1.2: General Von Neumann Architecture

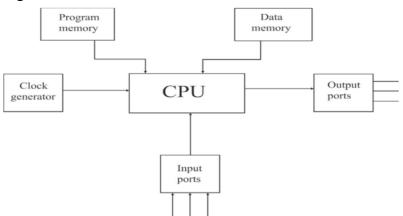

### 1.4 Basic Organization of Microprocessors

The basic components of a microcomputer are:

- 1. CPU

- 2. Program memory

- 3. Data memory

- 4. Output ports

- 5. Input ports

- 6. Clock generator

Figure1.3: Components of Microprocessors

### **Central Processing Unit**

The CPU consists of ALU (Arithmetic and Logic Unit), register unit and control unit. The CPU retrieves stored instructions and data wordfrom memory; it also deposits processed data in memory.

### a) ALU (Arithmetic and Logic Unit)

This section performs computing functions on data. These functions are arithmetic operations such as additions subtraction and logical operation such as AND, OR etc. Result are stored either in registers or in memory or sent to output devices.

### b) Register Unit

It contains various registers. The registers are used primarily to store data temporarily during the execution of a program. Some of the registers are accessible to the uses through instructions.

### c) Control Unit

It provides necessary timing & control signals necessary to all the operations in the microcomputer. It controls the flow of databetween the processor and peripherals (input, output & memory). The control unit gets a clock which determines the speed of the processor.

### The CPU has five basic functions

- 1) It fetches an instructions word stored in memory.

- 2) It determines what the instruction is telling it to do(decodes theinstruction).

- 3) It executes the instruction. Executing the instruction mayinclude same of the following major tasks:

- a. Transfer of data from reg. to reg. in the CPU itself.

- b. Transfer of data between a CPU reg. & specified memorylocation.

- c. Performing arithmetic& logical operations on datafrom aspecific memory location or a designated CPU registers.

- d. Directing the CPU to change a sequence of fetchinginstruction, if processing the data created a Specific conditions.

- e. Performing housekeeping function within the CPU itself inorder to establish desired condition at Certain registers.

- 4) It looks for control signal such as interrupts and provides appropriate responses.

- 5) It provides states, control, and timing signals that the memoryand input/output section can use.

### **Program Memory**

The basic task of a microcomputer system is to ensure that its CPU executes the desired instruction sequence is the programproperly. The instruction sequence is stored into the program memory on initialization- usually a power up and manual reset the processor starts by executing the instruction in a predetermined location inprogram memory. The first instruction of the program should therefore be in this location in typical  $\mu$ p basic system, the program tobe executed is fixed one which does not change. Therefore  $\mu$ -program are store on ROM, or PROM, EPROM, EEPROM. In the trainer kit, ROM contains only the monitor program. The user program is not stored in ROM because it needs not to be stored permanently.

#### **Data Memory**

A microcomputer manipulates data according to the algorithm given by the instruction in the program in the program memory. These instructions may require intermediate results to be stored, the functional block in µc have same internal register which can also be used if available for such storage external data memory is needed if the storage requirements are more. Apart from intermediate storage, the data memory may also beused to provide data needed by the program, to store some of the results of the program. Data memory is used for all storage purposesother than storage of program. Therefore, they must have head write capability R/WM or RAM. It stores both the instructions to be executed (i.e. program) and the data involved. It usually contains ROM (Read memory). The ROM can only read and can not be written into and is non-volatile that is, itretains its contents when the power is turned off. A ROM is typically used to store instructions and data that do not change. For example, it stores the monitor program if a microcomputer. One can either read from or write into a R/WM. The RWM is volatile, that is it does not retain its contents when the power is turned off. It is used to store user programmers & data which are temporary and might change during the course of executing a program. During a memory read operation, the content of the addressed location is not destroyed. During a unit operation, the original content of the addressed location is destroyed. Both ROM & R/WM are arranged into words, each of which has a unique address. The address of a word is memory location and it isplaced in parentheses. Therefore, X is an address and (X) is the control unit and select the proper memory location and obtaining its content takes a certain amount of time, this time is the access time of the memory. The access time affects the speed of the computer, pins, and the computer must obtain the instruction and data from the memory. Computer memory as usually RAM so that all memory locations have the same access time. The computer must wait shiner of unit's memory, typical memory access time range from several uses. Memory sections often sub-divided into units called pages. The entire memory section may involve millions of cords, when a page contains between 256 & 4k warts. The computer may access a memory location by first decreasing a particular page and the accessing a location on that page. The advantage of paging is that the computer can reach several locations on the same page with just address in the page. The process is like describing street address by first specifying aspect and them listing the have numbers. The control section transfers data to or from memory as follows.

- 1. The control section reads an address to the memory.

- 2. The control section sends a read and write signal to thememory to indicate, the direction of the transform.

- 3. The control section waits until transfer has beencompleted. This delay precedes the actual data's transferring the input case andfollows it in the output case.

### **Input/output Ports**

The input & output ports provide the microcomputer the capability to communicate with the outside world. The input ports allow data to pass from the outside world to the microcomputer data which will be used in the data manipulation being done by the microcomputer to send data to output devices. The user can enter instruction (i.e. program) and data inmemory through input devices such as keyboard, or simple switches, CRT, disk devices, tape or card readers. Computers are also used to measure and control physical quantities like temperature, pressure, speed etc. For these purposes, transducers are used to convert physical quantity into proportional electrical signals A/D computersare used to convert electrical signals into digital

signals which aresent to the computer. The computer sends the results of the computation to theoutput devices e.g. LED, CRT, D/A converters, printers etc. These I/O devices allow the computer to communicate with the outside world I/O devices are called peripherals.

### **Clock Generator**

Operations inside the  $\mu$ p as well as in other parts of the  $\mu$ c, are usually synchronous by nature. The clock generator generates the appropriate clock periods during which instruction executions arecarried out by the microprocessor. This condition ensures that different path of the systems can proceed in a systematic fashion. Some of the microprocessors have an internal clock generator circuit to generate a clock signal. These microprocessors require an external crystal or RC network to be connected at the appropriate pins for deciding the operating frequency (e.g. 8085). Some microprocessors require an external clock generator (e.g. 8086). These microprocessors also provide an output clock signal which can be used by other devices in the microcomputer system for their can timing and synchronizing.

### 1.5 Types of Microprocessor

There are basically 5 kinds of microprocessors :

**Complex Instruction Set Microprocessors:** They are also called as CISM in short and they categorize a microprocessor in which orders can be executed together along with other low-level activities. It mainly performs the task of uploading, downloading and recalling data into and from the memory card. Apart from that it also does complex mathematical calculations within a single command.

**Reduced Instruction Set Microprocessor :** This processor is also called as RISC in short. These kinds of chips are made according to the function in which the microprocessor can carry out small things within a particular command. In this way it completes more commands at a faster rate.

**Superscalar Processors :** This is a processor that copies the hardware on the microprocessor for performing numerous tasks at a time. They can be used for arithmetic and as multipliers. They have several operational units and thus carry out more than a one command by constantly transmitting various instructions to the

superfluous operational units inside the processor.

**The Application Specific Integrated Circuit :** This processor is also known as ASIC. They are used for specific purposes that comprises of automotive emissions control or personal digital assistant computer. This kind of processor is made with proper specification but apart from that it can also be made using the off the shelf gears.

**Digital Signal Multiprocessors :** Also called as DSP's, these are used for encoding and decoding videos or to convert the digital and video to analog and analog to digital. They need a microprocessor that is excellent in mathematical calculations. The chips of this processor are employed in SONAR, RADAR, home theaters audio gears, Mobile phones and TV set top boxes.

### Unit: 2

### **Components of Microprocessor**

### 2.1 I/O (Input/Output)

I/O (input/output) communicates with the outside world. I/O includes two types of devices: input and output; these I/O devices are known as peripherals. The input devices such as keyboard, switches, and an analog to digital (A/D) converter transfer binary information (data and instructions) from the outside world to the microprocessor. The output devices transfer data from the microprocessor to the outside world. They include devices such as light emitting diodes (LEDs), the cathode ray tube (CRT) or video screen, a printer, etc.  $\mu$ Cs(PCs) are generally equipped with output devices such as video screen(monitors) and a printer.

### 2.2 Memory

Memory stores such binary information as instructions and dataand provides that information to the microprocessor whenever necessary. To execute programs, the microprocessor reads instructions and data from the memory and performs the computing operations in its ALU section. Results are either transferred to the output section for display or stored in memory for later use.

Memory can be classified into two groups: Primary (system or main) memory and Secondary (storage) memory.

### 2.2.1 Primary Memory

This is the memory the microprocessor uses in executing and storing programs. This memory should be able to respond fast enough to keep up with the execution speed of the microprocessor. Therefor it should be random access memory, meaning that the microprocessor should be able to access information from any register with the same speed(independent of its place in the chip). The size of the memory chip is specified in terms of bits.Forexample,1K memory chip means it can store 1024 bits(not bytes).Examples of primary memory are R/WM (RAM) and ROM.

### 2.2.2 Secondary Memory

The other group is the storage memory, such as magnetic disks and tapes. This memory is used to store programs and results after the completion of program

execution. Information stored in these memories is nonvolatile, meaning information remains intact even if the system is turned off. The microprocessor cannot directly execute or process programs stored in these devices; programs need to be copied into the primary memory first. Therefor the size of primary memory, such as 512K or 8M (megabytes), determines how large a program the system can process. The size of the storage memory is unlimited; when one disk or tape is full, the next one can be used.

### 2.2.3 Cache Memory

Cache memory is a very high-speedsemiconductor memory which can speeds up the CPU. It acts as a buffer between the CPU and the main memory. It is used to hold those parts of data and program which are most frequently used by the CPU. The parts of data and programs are transferred from the disk to cache memory by the operating system, from where the CPU can access them.

### 2.3 PROCESSOR UNIT

The Microprocessor in many ways similar to the CPU, but includes all the logic circuitry, including the control unit, on one chip. The microprocessor can be divided into three segments for the sake of clarity: arithmetic/logic unit (ALU), register array and control unit.

**Arithmetic/Logic Unit:** This is the area of the microprocessor where various computing functions are performed on data. The ALU unit performs such arithmetic operations as addition and subtraction, and such logic operations as AND, OR and exclusive OR etc.

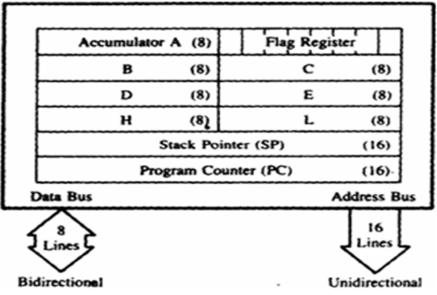

**Register Unit:** This area of microprocessor consists of various registers identified by letters such as B, C, D, E, H, L. These registers are primarily used to store data temporarily during the execution of a program and are accessible to the user through instructions. These registers are also called general purpose registers. So, there are all together six general purpose registers in 8085 Microprocessor.

**Control Unit:** The control unit provides the necessary timing and control signals to all the operation in the microcomputer. It controls the flow of data between the microprocessor and memory and peripherals.

### 2.4 Bus Structure of 8085

A *bus* in a microprocessor-based system is defined as a group of separate wires which work together to perform a particular task. A microprocessor-based system, or <u>microcomputer</u>, has three buses which combine to transfer information between the microprocessor and other parts of the system, such as memory or input/output devices. Typical tasks performed by these buses include selecting the source or destination location address for a data transfer, actually moving the data from one part of the system to another, and finally, controlling and synchronizing the electronic devices involved in the data transfer process.

There are three buses in Microprocessor:

- 1. Address Bus

- 2. Data Bus

- 3. Control Bus

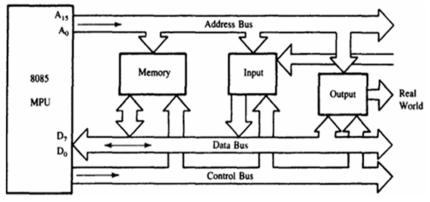

Fig2.1: 8085 Bus Structure

1. Address Bus: Generally, microprocessor has 16-bit address bus(A<sub>0</sub>-A<sub>15</sub>). The bus over which the CPU sends out the address of the memory location is known as Address Bus. The address bus carries the address of the memory location to be written or to be read from. The address bus is unidirectional. It means bit flowing occurs only in one direction, only from the microprocessor to the peripheral devices.

We can find how much memory location is using by microprocessor by the formula  $2^{N}$  where N is the number of bits used for address lines.

Here  $2^{16} = 65536$  bits or 64KB. So, we can say 8085 can access 64KB of memory locations.

Let us try this question "If a processor has 4GB of memory then how many address lines are required to access this memory? Ans is 32 lines you need to find this by your own.

- 2. Data Bus: 8085 microprocessor has 8-bit data buses. So, it can be used to carry 8 bits of data starting from 0000000(00H) to 11111111(FFH). Here H tells hexadecimal number. The data buses are bidirectional. These lines are used for data flowing in both direction means data can be transferred or received through these lines. The data bus also connects I/O ports and the CPU. The largest number that can be appeared in the bus is 1111111. It has 8 parallel lines of data bus so it can access upto 2<sup>8</sup>=256 data bus lines.

- **3. Control Bus:**The control bus is used for sending control signals to the memory and I/O devices. The CPU sends control signal on the control bus to enable the outputs of addressed memory devices or I/O port devices.

Some of the control bus signals are as follows:

- a) Memory read

- b) Memory Write

- c) I/O read

- d) I/O Write

### Unit: 3

### **Instruction Cycle**

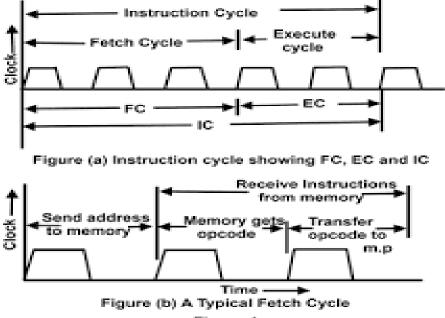

### 3.1 Instruction cycle, Machine cycle & T-states

*Instruction cycle*: is defined as the time required completing the execution of an instruction. The 8085 instructions cycle consists of one to six machine cycles or one to six operations.

*Machine cycle:* is defined as the time required to complete one operation of accessing memory, I/O, or acknowledging the external request. This cycle may consist of 3 to 6 T states.

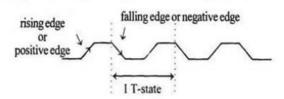

T states: is defined as one subdivision of the operation performed in one clock period. These subdivisions are internal states synchronized with the system clock, and each T-state precisely equal to one clock period. The term T-states and clock period are often used synonymously.

|                       |      | Status         |                |                                                                 |

|-----------------------|------|----------------|----------------|-----------------------------------------------------------------|

| Machine Cycle         | IO/M | S <sub>1</sub> | S <sub>0</sub> | <b>Control Signals</b>                                          |

| Opcode Fetch          | 0    | 1              | 1              | $\overline{RD} = 0$                                             |

| Memory Read           | 0    | 1              | 0              | $\overline{RD} = 0$                                             |

| Memory Write          | 0    | 0              | 1              | $\overline{WR} = 0$                                             |

| I/O Read              | 1    | 1              | 0              | $\overline{\text{RD}} = 0$                                      |

| I/O Write             | 1    | 0              | 1              | $\overline{WR} = 0$                                             |

| Interrupt Acknowledge | 1    | 1              | 1              | $\overline{INTA} = 0$                                           |

| Halt                  | Z    | 0              | 0 ]            |                                                                 |

| Hold                  | Z    | Х              | x              | $\overline{RD}$ , $\overline{WR} = Z$ and $\overline{INTA} = Z$ |

| Reset                 | Z    | Х              | x              |                                                                 |

3.2 Machine cycle of 8085 microprocessor

8085 Machine Cycle Status and Control Signals

NOTE: Z = Tri-state (high impedance)

X = Unspecified

Fig3.1 8085 Machine cycle status and control signals

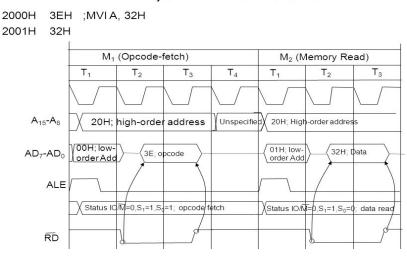

### 3.2.1 Opcode Fetch Machine Cycle

Each instruction of the processor has one-byte Opcode. The Opcodes are stored in memory. So, the processor executes the Opcode fetch machine cycle to fetch the Opcode from memory. Hence, every instruction starts with Opcode fetch machine cycle. The time taken by the processor to execute the Opcode fetch cycle is 4T.

In this time, the first, 3T-states are used for fetching the Opcode from memory and the remaining T-states are used for internal operations by the processor.

### 3.2.2 Memory Read Machine Cycle

The memoryread machine cycle is executed by the processor to read a data byte from memory.The processor takes 3Tstates to execute thiscycle.The instruction which have more than one-byte word size will use the machine cycle after the Opcode fetch machine cycle.

### **3.2.3 Memory Write Machine Cycle**

The memory write machine cycle is executed by the processor to write a data byte in a memory location. The processor takes, 3T states to execute this machine cycle

### 3.2.4 I/O Read Machine Cycle

The I/O Read cycle is executed by the processor to read a data byte from I/O port or from the peripheral, which is I/O, mapped in the system. The processor takes 3T states to execute this machine cycle. TheIN instruction uses this machine cycle during the execution.

### 3.2.5 I/O Write Machine Cycle

The I/O write machine cycle is executed by the processor to write a data byte in the I/O port or to a peripheral, which is I/O, mapped in the system. The processor takes 3T states to execute this machine cycle.

### 3.3 Timing Diagram

It is a graphical representation. It represents the execution time taken by each instruction in a graphical format. The execution time is represented in T-states.

Time period, T = 1/f; where f = Internal clock frequency

Figure 3.2: Clock Signal

- Opcode fetch cycle (4T)

- Memory read cycle (3 T)

- Memory write cycle (3 T)

- I/O read cycle (3 T)

- I/O write cycle (3 T)

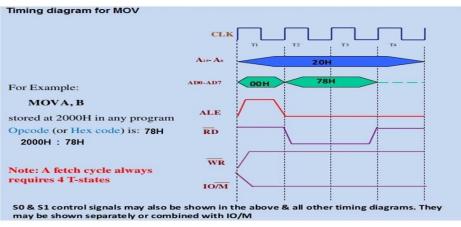

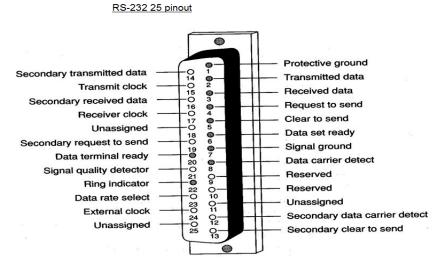

Fig3.3 Timing diagram of MOV instruction cycle

The instruction MOV A,B is a 1-byte instruction. Its operation is to copy the content of B in A register. The Microprocessor takes only one machine cycle(OPCODE Fetch) to complete instruction. Hence, Hex code for MOV A,B is passed to the microprocessor.There are 4T-states.

### T-1 state

During the T1 state, the contents of the program counter are placed on the 16-bit address bus. The higher order 8 bits are transferred to the address bus(A8-A15) and the lower order 8 bits are transferred to the Multiplexed A/D(AD0-AD7) bus.

### ALE(address latch enable)

As soon as ALE goes high, the memory latches the AD0-AD7 bus. At the middle of the T-state the ALE goes low.

### T-2 state

During the beginning of the state, the RD' signal goes low to enable memory. During this state, the selected memory location is placed on D0-D7 of the Address/Data multiplexed bus. The Opcode(78H)) is placed in the AD7-AD0 bus.

### T3-State

In this state the cycle, the Opcode(78H)) of the A/D bus is transferred to the instruction register in the microprocessor. Now the RD' goes high after this action and thus disables the memory from A/D bus.

T4-State: In this state the Opcode which was fetched from the memory is decoded.

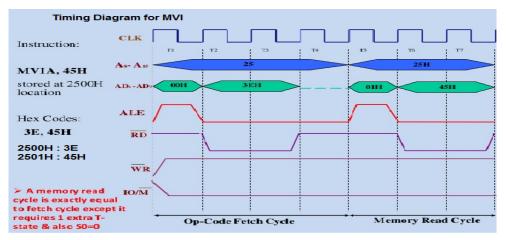

Fig 3.4: Timing diagram of MVI instruction cycle

**MVI A, 45H** means to immediately load the data 45h to register A of the microprocessor. It is a 2-byte instruction.

The first machine cycle is Opcode fetch and the second is memory read cycle, we have already discussed about Opcode fetch now we will discuss on Memory read cycle.

During the T5, T6 and T7 states the A8-A15 address bus carry the higher bit(25H) of the program counter address(2501H).

During T5 states as the ALE goes high the AD0-AD7 will carry the lower bit(01H) of the program counter address(2501H)

During T6 & T7 states the ALE goes low enabling the data bus and it will read(RD'=0) the data 45H from memory.

Note: please refer to the machine cycle table to know the status of IO/M and S0, S1 signal status for corresponding machine cycle.

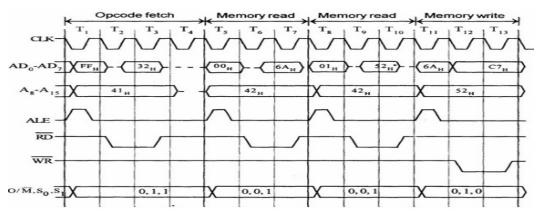

### **Timing Diagram of STA**

STA stands for store the content of Accumulator to the given location. Let us take an example of STA 526AH, where the content of Accumulator will store in the location 526AH.

| Address | Mnemonics          | Opcode |

|---------|--------------------|--------|

| 41FF    | STA                | 32H    |

| 4200    | Lower bit address  | 6AH    |

| 4201    | Higher bit address | 52H    |

|         | Table 3 1          |        |

Table:3.1

It requires 4 machine cycles and 13 T states.

a) Opcode fetch (4T) b) Memory Read (3T)c.) Memory Read (3T) d.) Memory Write(3T)

Fig3.5:Timing diagram of STA instructions

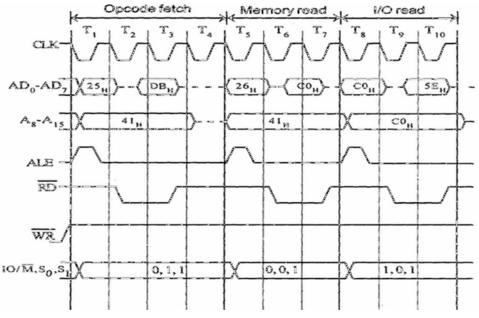

### **Timing Diagram of IN**

IN port address refers to input to Accumulator from I/O port. It requires 3 M/C and 10 T states. Let us take example of IN C0H. The following operation are carried out.

- Fetching the Opcode DBH from the memory 4125H.

- Read the port address C0H from 4126H.

- Read the content of port C0H and send it to the accumulator.

- Let the content of port is 5EH.

| Address | Mnemonics | Op code |

|---------|-----------|---------|

| 4125H   | IN        | DBH     |

| 4126H   |           | СОН     |

Fig:3.6Timing diagram for IN C0Hinstruction cycle

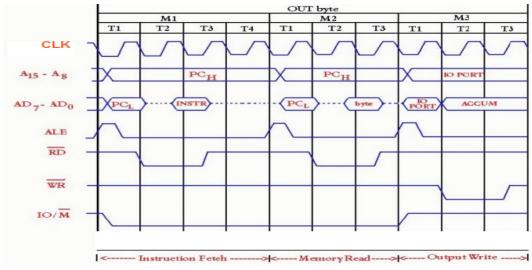

### Timing diagram for OUT

OUT port address it stands for output from accumulator to I/O port. It also requires 3 machines cycles and 10 T states. The machine cycles are: a.) Opcode fetch (4T)b.) Memory Read (3T)c.) I/O write (3T)

#### .. Table : 3.2

Fig 3.7 Timing diagram of OUT

### Numerical

**Example :** Calculate the total execution to execute the instruction MVI B, 05H. Let the clock frequency of the microprocessor be 3.125 MHZ.

### Solution

| Mnemonic | Instruction byte | Machine Cycle       | T states |

|----------|------------------|---------------------|----------|

| MVI B    | Opcode           | Opcode Fetch        | 4T       |

| 05H      | Immediate Data   | Read Immediate Data | 3T       |

Here total T states =4T+3T=7T

Clock frequency of microprocessor (f) = 3.125 MHZ

Time(T) for one clock =

$$\frac{1}{3.125 \text{ MHZ}} = 0.32 \text{ }\mu\text{s}$$

So, total execution time for instruction=7T

$$= 7*0.32 \ \mu s$$

= 2.24 µs

Therefor the microprocessor can execute MVI 05H in 2.24  $\mu s.$

Try It: (a) Calculate the execution time of (a) STA 2050H (b) LDA 4001H (c) MOV A,B

b) Draw timing diagram for LDA 2050H instruction 2050H hold data 5FH.

### Unit: 4

### **Intel 8085 Microprocessor**

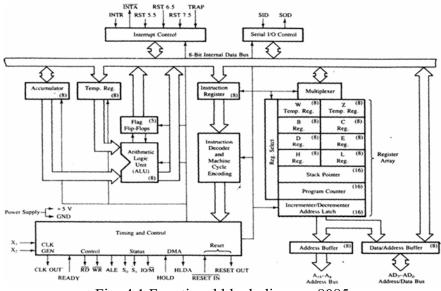

#### 4.1 Fnctional Block Diagram

Fig: 4.1 Functional block diagram 8085

### 4.2 Pin Configuration Of 8085

TABLE4.1: 8085 SIGNAL DESCRIPTION SUMMARY

| Pin Name                         | Description                      | Туре                    |

|----------------------------------|----------------------------------|-------------------------|

| ADa - ADa                        | Address / Data Bus               | Bidirectional, Tristate |

| A <sub>8</sub> - A <sub>15</sub> | Address Bus                      | Output, Tristate        |

| ALE                              | Address Latch Enable             | Output, Tristate        |

| RD                               | Read Control                     | Output, Tristate        |

| WR                               | Write Control                    | Output, Tristate        |

| 10/ M                            | 1/O or memory Indicator          | Output, Tristate        |

| S <sub>a</sub> , S <sub>1</sub>  | Bus State Indicator              | Output                  |

| READY                            | Wait state request               | Input                   |

| SID                              | Serial Input Data                | Input                   |

| SOD                              | Serial Output Data               | Output                  |

| HOLD                             | HOLD request                     | loput                   |

| HLDA                             | HOLD acknowledge                 | Output                  |

| INTR                             | Interrupt request                | Input                   |

| TRAP                             | Nonmaskable interrupt<br>request | Input                   |

| RST 5.5                          | Hardware vectored                |                         |

|                                  | Interrupt request                | Input                   |

| RST 6.5                          | Hardware vectored                |                         |

|                                  | Interrupt request                | Input                   |

| RST 7.5                          | Hardware vectored                |                         |

|                                  | Interrupt request                | Input                   |

| INTA                             | Interrupt acknowledge            | Output                  |

| RESET IN                         | System reset                     | Input                   |

| RESET OUT                        | Peripherals reset                | Output                  |

| X., X,                           | Crystal or RC Connection         | Input                   |

| CLK (OUT)                        | Clock Signal                     | Output                  |

| V., V.                           | Power, ground                    | and a second            |

Note : A overbar on the signal, indicates that it is active low, (i.e., the signal is tormally high and when the signal is activated it is low).

Fig 4.2: pin configuration 8085

### 4.3 Description of each blocks: Registers, Flag, Data and Address Bus, Timing and Control Unit, Interrupts

Accumulator: It is an 8-bit register which is used to perform arithmetical and logical operation. It stores the output of any operation. Italso works as registers for I/O accesses.

**Temporary Register:**-It is an 8-bit register which is used to hold the data on which the accumulator is computing operation. It is also called as operand register because it provides operands to ALU

**Registers**: These are general purposes registers. Microprocessor consists 6 general purpose registers of 8-bit each named as B, C, D, E, H and L. Generally, theses registers are not used for storing the data permanently. It carries the 8-bits data. These are used only during the execution of the instructions. These registers can also be used to carry the 16 bits data by making the pair of 2 registers. The valid register pairs available are BC, DE and HL. We cannot use other pairs except BC,DEand HL. These registers are programmed by the user.

Fig 4.3: Array of Registers

ALU: Algorithm Logical Units performs the arithmetic operations and logical operation.

Flag Registers: It consists of 5 flip flop which changes its status according to the result stored in an accumulator. It is also known as status registers. It is connected to the ALU.

There are five flip-flops in the flag register are as follows:

- 1. Sign(S)

- 2. Zero(z)

- 3. Auxiliary carry(AC)

- 4. Parity(P)

- 5. Carry(C)

The bit position of the flip flop in flag register is:

| D7 | D <sub>6</sub> | D۶ | D4 | D3 | $D_2$ | D1 | D <sub>0</sub> |

|----|----------------|----|----|----|-------|----|----------------|

| S  | Z              |    | AC |    | Р     |    | СҮ             |

All of the threeflip flop set and reset according to the stored result in the accumulator.

1. Sign(S)- If D7 of the result is 1 then sign flag is set otherwise reset. As we

know that a number on the D7 always decides the sign of the number. if D7 is 1: the number is negative. if D7 is 0: the number is positive.

- 2. Zeros(Z)-If the result stored in an accumulator is zero then this flipflop is set otherwise it is reset.

- **3.** Auxiliary carry(AC)-If any carry goes from D3 to D4 in the output then it is set otherwise it is reset.

- 4. **Parity(P)**-If the no of 1's is even in the output stored in the accumulator then it is set otherwise it is reset for the odd.

- 5. Carry(C)-If the result stored in an accumulator generates a carry in its final output then it is set otherwise it is reset.

**Instruction registers(IR):** It is a 8-bit register. When an instruction is fetched from memory then it is stored in this register.

**Instruction Decoder:** Instruction decoder identifies the instructions. It takes the information from instruction register and decodes the instruction to be performed.

**Program Counter**: It is a 16-bit register used as memory pointer. It stores the memory address of the next instruction to be executed. So, we can say that this register is used to sequencing the program. Generally the memory have 16-bit addresses so that it has 16 bit memory. The program counter is set to 0000H.

**Stack Pointer:** It is also a 16-bit register used as memory pointer. It points to the memory location called stack. Generally, stack is a reserved portion of memory where information can be stores or taken back together.

**Timing and Control Unit:-** It provides timing and control signal to the microprocessor to perform the various operation. It has three control signals. It controls all external and internal circuits. It operates with reference to clock signal. It synchronizes all the data transfers. There are three control signals:

- 1. **ALE**-Arithmetic Latch Enable, itprovides control signal to synchronize the components of microprocessor.

- 2. **RD**-This is active low used for reading operation.

- 3. **WR**-This is active low used for writing operation.

There are three status signals used in microprocessor S0, S1 and IO/M. It changes

| IO/M(Active<br>Low) | <b>S1</b> | S2 | Data Bus Status(Output) |

|---------------------|-----------|----|-------------------------|

| 0                   | 0         | 0  | Halt                    |

| 0                   | 0         | 1  | Memory WRITE            |

| 0                   | 1         | 0  | Memory READ             |

| 1                   | 0         | 1  | IO WRITE                |

| 1                   | 1         | 0  | IO READ                 |

| 0                   | 1         | 1  | Opcode fetch            |

| 1                   | 1         | 1  | Interrupt acknowledge   |

its status according the provided input to these pins.

Fig 4.4: Timing and control signals

**Serial Input Output Control-** There are two pins in this unit. This unit is used for serial data communication.

### Interrupt Unit

An interrupt is a signal to the processor emitted by hardware or software indicating an event that needs immediate attention. An interrupt alerts the processor to a highpriority condition requiring the interruption of the current code the processor is executing. The processor responds by suspending its current activities, saving its state, and executing a function called an interrupt handler (or an interrupt service routine, ISR) to deal with the event. This interruption is temporary, and, after the interrupt handler finishes, the processor resumes normal activities. There are two types of interrupts: hardware interrupts and software interrupts. We will discuss in unit7 about the interrupts and their priority.

There are 6 interrupt pins in this unit. Generally, an external hardware is connected to these pins. These pins provide interrupt signal sent by external hardware to microprocessor and microprocessor sends acknowledgement for receiving the interrupt signal. Generally, INTA is used for acknowledgement.

Register Section: Many registers have been used in microprocessor.

### 4.4. Instructions- Opcode and Operands

### \*What is Instruction?

An instruction is a binary pattern designed inside the microprocessor to perform a specific function. In other words, it is actually a command to the microprocessor to perform a given task on specified data.

### **Instruction Set**

The entire group of these instructions are called instruction set. The <u>instruction</u> <u>set</u>determines what functions the <u>microprocessor</u> can perform.

### **Instruction Format**

| Opcode | Operand |

|--------|---------|

|--------|---------|

Each instruction has two parts: one is the task to be performed called the operation code (opcode) and the other is the data to be operated on called the operand (data).

### Instruction and Word Size

1. One word or one-byte Instruction

It includes the opcode and operand in the same byte.

### Example: ADD B

2. Two word or two-byte Instruction

First byte specifies the opcode and second byte specifies the operand.

Example: MVI A, 05

3. Three word or three-byte Instruction

The first byte specifies the opcode and the following two bytes specify the 16-bit address. The second byte is lower order and the other is higher order.

Example: JMP 2085H

### 4.5 Addressing Modes in 8085

Addressing modes Instructions are command to perform a certain task in

microprocessor. The instruction consists of op-code and data called operand. The operand may be the source only, destination only or both of them. In these instructions, the source can be a register, a memory or an input port. Similarly, destination can be a register, a memory location, or an output port. The various format (way) of specifying the operands are called addressing mode. So, addressing mode specifies where the operands are located rather than their nature. The 8085 has 5 addressing modes:

### 1) Direct addressing mode

The instruction using this mode specifies the effective address as part of instruction. The instruction size either 2-bytes or 3-bytes with first byte op-code followed by 1 or 2 bytes of address of data.

e.g.

LDA 9500H; A ← [9500H]

IN 40H; A ← [40H]

This type of addressing is called absolute addressing.

### 2) Register direct addressing mode

This mode specifies the register or register pair that contains the data.

e.g.

MOV A, B

ADD H

XOR C etc.

### 3) Register indirect addressing mode

In this mode the address part of the instruction specifies the memory whose contents are the address of the operand. So, in this type of addressing mode, it is the address of the address rather than address itself.

e.g. MOV A, M, STAX B etc.

### 4) Immediate addressing mode

In this mode, the operand position is the immediate data. For 8-bit data, instruction

size is 2-bytes and for 16-bit data, instruction size is 3-bytes.

E.g. MVI A, 32H, LXI B, 4567H, SBI 76H etc.

#### 5) Implied or Inherent addressing mode:

The instructions of this mode do not have operands. E.g. NOP: No operation HLT: Halt EI: Enable interrupt DI: Disable interrupt.

# Unit: 5

# **Programming with Intel 8085 Microprocessor**

#### 5.1 Instruction format and data format

An 8085program instructions format may be one, two or three length.

#### 1. 1-byte instruction (8 bit)

1-byte instructionincludesoperand and opcode in the same byte. It occupies 1-byte space in memory.

| 1 |  |  |  |  |

|---|--|--|--|--|

|   |  |  |  |  |

#### E.g.

#### **Opcode operand**

| MOV | A, B |

|-----|------|

| ADD | В    |

| CMA |      |

#### 2. Byte instruction (16 bit)

In a 2-byte instruction, the first byte specifies the operation and second byte specifies opcode. It occupies 2-byte space in memory

#### Opcode

DATA OR ADDRESS

E.g.

| Opcode | Operand |

|--------|---------|

| MVI    | A, 45H  |

| MVI    | B, F2H  |

#### 3. **3-byte instruction**

In 3-byte instruction the first byte specifies the opcode and following two byte

specifies the 16-bit address. It occupies 3-byte space in memory.

E.g.

| Opcode | Operand | Hex code |

|--------|---------|----------|

| LDA    | 2050Н   | 3A       |

|        |         | 50       |

|        |         | 20       |

| JMP    | 2085H   | C3       |

|        |         | 85       |

|        |         | 20       |

## **Instruction with a Memory Address**

Operation: go to address 2085.

Instruction: JMP 2085

Opcode: JMP

Operand: 2085

## **Binary code**

| 1100 0011 | C3 | 1 <sup>st</sup> byte   |

|-----------|----|------------------------|

| 1000 0101 | 85 | 2 <sup>nd</sup> byte   |

| 0010 0000 |    | 203 <sup>rd</sup> byte |

## Data Format

In 8085, data stores in the form of 8-bit binary integer. In the Intel 8085, bit 0 is referred as the least signification bit (LSB) and bit 7 is referred as most signification bit (MBS).

## Data can be represented in four formats

ASCII (American Standard Code for Information Interchange) e.g. - A-Z, az, 0-9 etc.

- 2. BCD (Binary Code Decimal) e.g. 0-F

- 3. Signed Integer e.g. +2, +3,

- 4. Unsigned Integer e.g. -2, -3,

# Assume the accumulator contains the following value: 0100 0001

There are four ways of reading this value:

It is an unsigned integer expressed in binary; the equivalent decimal number would be 65.

It is a number expressed in BCD (Binary Coded Decimal) format. That would make it, 41.

It is an ASCII representation of a letter. That would make it the letter A.

It is a string of 0's and 1's where the 0th and the 6th bits are set to 1 while all other bits are set to 0.

# 5.2 Intel 8085 instruction Set& Instructions types

An Instruction is a command given to the computer to perform a specified operation on given data. The instruction set of a microprocessor is the collection of the instructions that the microprocessor is designed to execute. The instructions described here are of Intel 8085. The *instruction set* of the 8085 microprocessor consists of 74 instructions with 246 different bit patterns. These instructions are of Intel Corporation. They cannot be used byother microprocessor manufactures. The programmer can write a program in assembly language using these instructions. These instructions have been classified as below:

# 1. Data transfer instruction

This instruction copies data from one location to another location. There are various types of data transfers.

Between register

E.g. MOV A, B; MOV C, B etc.

Specify the data byte to register or memory location.

E.g. MVI B, 23H; LDA 2500H etc.

Between memory location and register

E.g. LXI 2050H

Between input and output

E.g. IN 02H; OUT PORT1 etc.

#### 2. Arithmetic instruction

This instruction performs arithmetic operation such as addition, subtraction, increment, and decrement. E.g. ADD B, ADI 25H, SUB C, SUI 23H, SUB M, INR B, DCR A etc.

#### Addition (ADD, ADI)

- Any 8-bit number.

- The contents of a register.

- The contents of a memory location.

- Can be added to the contents of the accumulator and the result is stored in the accumulator.

## Subtraction (SUB, SUI)

- Any 8-bit number

- The contents of a register

- The contents of a memory location

- Can be subtracted from the contents of the accumulator. The result is stored in the accumulator.

## Increment (INR) and Decrement (DCR)

- The 8-bit contents of any memory location or any register can be directly incremented or decremented by 1.

- No need to disturb the contents of the accumulator

## 3. Logical instruction

This instruction performs logical operation like AND, OR, COMPARE, ROTATED.

CMP- compare RAL- rotation left

RAR- rotation right

ANA- AND

ORA- OR

These instructions perform logic operations on the contents of the accumulator – ANA, ANI, ORA, ORI, XRA and XRI

# • Source: Accumulator and

- An 8-bit number

- The contents of a register

- The contents of a memory location

# • Destination: Accumulator

| ANA R/M | AND Accumulator withReg/Mem          |

|---------|--------------------------------------|

| ANI #   | AND Accumulator With an 8-bit number |

| ORA R/M | OR Accumulator withReg/Mem           |

| ORI #   | OR Accumulator With an 8-bit number  |

| XRA R/M | XOR Accumulator withReg/Mem          |

| XRI #   | XOR Accumulator With an 8-bit number |

- Complement

- 1's complement of the contents of the accumulator. CMA No operand

- Rotate Rotate the contents of the accumulator one position to the left or right.

- RLC Rotate the accumulator left. Bit 7 goes to bit 0AND the Carry flag.

- RAL Rotate the accumulator left through the carry. Bit 7 goes to the carry and carry goes to bit 0.

- RRC Rotate the accumulator right. Bit 0 goes to bit 7 AND the Carry flag.

- RAR Rotate the accumulator right through the carry. Bit 0 goes to the carry and carry goes to bit 7.

#### • Compare

- Compare the contents of a register or memory location with the contents of the accumulator.

- CMP R/M compares the contents of the register or memory location to the contents of the accumulator.

- CPI # Compare the 8-bit number to the contents of the accumulator.

- The compare instruction sets the flags (Z, Cy, and S).

- The compare is done using an internal subtraction that does not change the contents of the accumulator.

A –(R / M / #)

#### 4. Branch instruction

Two types

#### **Unconditional branch**

Go to a new location no matter what.

#### **Conditional branch**

Go to a new location if the condition is true.

## **Unconditional Branch**

- JMP Address Jump to the address specified (Go to).

- CALL Address Jump to the address specified but treat it as a subroutine.

- RET Return from a subroutine.

- The addresses supplied to all branch operations must be 16-bits.

#### **Conditional Branch**

– Go to new location if a specified condition is met.

JZ Address (Jump on Zero) - Go to address specified if the Zero flag is set.

JNZ Address (Jump on NOT Zero) – Go to address specified if the Zero flag is not set.

JC Address (Jump on Carry) - Go to the address specified if the Carry flag is set.

JNC Address (Jump on No Carry) – Go to the address specified if the Carry flag is not set.

JP Address (Jump on Plus) – Go to the address specified if the Sign flag is not set

JM Address (Jump on Minus) - Go to the address specified if the Sign flag is set.

## 5. Machine Control

## – HLT

Stop executing the program. - NOP

No operation

Exactly as it says, do nothing.

Usually used for delay or to replace instructions during debugging.

These instruction control machines function such as HLT, NOP, and EI etc.

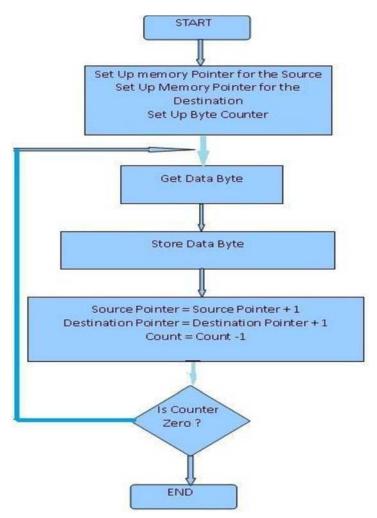

## 5.3 Assembly language program and flowchart

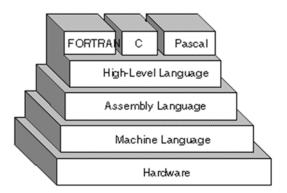

# fig:5.1: programming languages

A vocabulary and set of grammatical rules for instructing a computer to perform specific tasks. The term programming language usually refers to high-level languages, such as BASIC, EDA, FORTAN C, C++ etc. Each language has a unique set of keywords (words that it understands) and a special syntax for organizing programming instructions.

High-level programming languages, while simple compared to human languages, are more complex than the languages the computer actually understands,

called machine languages. Each different type of CPUhas its own unique machine language.

Lying between machine languages and high-level languages are languages called assembly languages. Assembly languages are similar to machine languages, but they are much easier to program in because they allow a programmer to substitute names for numbers. Machine languages consist of numbers only.

Lying above high-level languages are languages called fourth-generation languages (usually abbreviated 4GL). 4GLs are far removed from machine languages and represent the class of computer languages closest to human languages.

Regardless of what language you use, you eventually need to convert your program into machine language so that the computer can understand it. There are two ways to do this:

- 1) Compile the program

- 2) interpret the program

The question of which language is best is one that consumes a lot of time and energy among computer professionals. Every language has its strengths and weaknesses. For example, FORTRAN is a particularly good language for processing numerical data, but it does not lend itself very well to organizing large programs. Pascal is very good for writing well-structured and readable programs, but it is not as flexible as the C programming language. C++ embodies powerful object-oriented features, but it is complex and difficult to learn.

The choice of which language to use depends on the type of computer the program is to run on, what sort of program it is, and the expertise of the programmer.

Flowchart: 1. it is a diagram of the sequence of operations in a computer program.

2. This means that you should create your flow diagram such that anyone could implement the program

in any programming language. Thus, a flow diagram or chart is independent of the programming language.

#### **Flow Chart**

| Name                      | Symbol             | Description                                                                  |  |

|---------------------------|--------------------|------------------------------------------------------------------------------|--|

| Process                   |                    | Process or action step                                                       |  |

| Flow line                 |                    | Direction of process flow                                                    |  |

| Start/ terminator         |                    | Start or end point of process flow                                           |  |

| Decision Represe<br>point |                    | Represents a decision making point                                           |  |

| Connector                 | Ó                  | Inspection point                                                             |  |

| Inventory                 | $\bigtriangledown$ | Raw material storage                                                         |  |

| Inventory                 | $\wedge$           | Finished goods storage                                                       |  |

| Preparation               |                    | Initial setup and other<br>preparation steps before start of<br>process flow |  |

| Alternate process         |                    | Shows a flow which is an alternative to normal flow                          |  |

| Flow line(dashed)         |                    | Alternate flow direction of<br>information flow                              |  |

Fig5.2: Flowchart.

#### Microprocessor program

#### #) Program-01

Write a program to store data type 32H into memory location.

| MVI A, 32H | : store 32H in the accumulator.                |

|------------|------------------------------------------------|

| STA 2000H  | : copy accumulator content to memory location. |

| HLT        | : stop                                         |

#### #) Program-02

Write a program to store data of register B into memory location 4000H.

MOV A, B STA 4000H HLT

#### #) Program-03

Write a program to exchange the content of memory location 2000H and 4000H.

| LDA 2000H | : get the content of memory location 2000H into accumulator    |

|-----------|----------------------------------------------------------------|

| MOV B, A  | : save the content into B.                                     |

| LDA 4000H | : get the content of memory location 4000H into accumulator    |

| STA 2000H | : store the content of accumulator at 2000H.                   |

| MOV A, B  | : save the content back to accumulator.                        |

| STA 4000H | : store the content of accumulator into memory location 4000H. |

| HLT       | : stop                                                         |

#### #) Program-04

Write a program to add two numbers.

| 14H                     |

|-------------------------|

| 89H                     |

| 14+89=9D (Result)       |

| HL point 2000H.         |

| get first operand.      |

| HL points 2001H.        |

| Add                     |

| HL points 2002H.        |

| store the result 2003H. |

| stop.                   |

|                         |

#### #) Program-05

Write a program to subtract two numbers.

| 51H                       |

|---------------------------|

| 19H                       |

| 51-19=38H (Result)        |

| : HL point 4000H.         |

| : get first operand.      |

| : HL points 4001H.        |

| : Add                     |

| : HL points 4002H.        |

| : store the result 4003H. |

| : stop.                   |

|                           |

#### #) Program-06

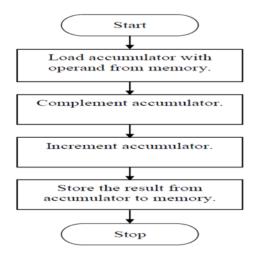

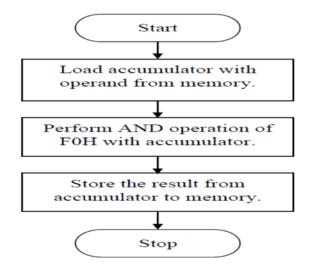

Write a program to find the 1's complements of the number stored at memory location 4400H and stored the complements number at memory location 4300H.

| 4400H     | 55H                  |

|-----------|----------------------|

| 4300H     | AAH (Result)         |

| LDA 4400H | : get the number     |

| СМА       | : complement         |

| STA 4300H | : stored the result. |

| HLT       | : stop               |

#### #) Program-07

Write a program to find the 1's complements of the number stored at memory location 4400H and stored the complements number at memory location 4300H.

| 4400H     | 55H                      |

|-----------|--------------------------|

| 4300H     | AAH+1= ABH (Result)      |

| LDA 4400H | : get the number         |

| СМА       | : complement             |

| ADI, 01H  | : add one in the number. |

| STA 4300H | : stored the result. |

|-----------|----------------------|

| HLT       | : stop               |

#### #) Program-08

Write a program to shift an 8-bit data four bits right. Assume that the data is in the register C.

MOV A, C RAR RAR RAR MOVC, A HLT

#### #) Program -09

Write a program to find the larger of two 8-bit numbers.

| LXI H, 3000H | : Load the H-L pair with address 3000H.          |

|--------------|--------------------------------------------------|

| MOV A, M     | : copy the content of memory to acc.             |

| INX H        | : increment H-L pair.                            |

| MOV B, M     | : copy the content of memory to register B.      |

| CMP B        | : compare B with A.                              |

| JNC 200BH    | : jump to the address 200B if there is no carry. |

| MOV A, B     | : move registers B to A.                         |

| INX H        | : increment H-L pair.                            |

| MOV M, A     | : move acc. to memory.                           |

| HLT          | : stop                                           |

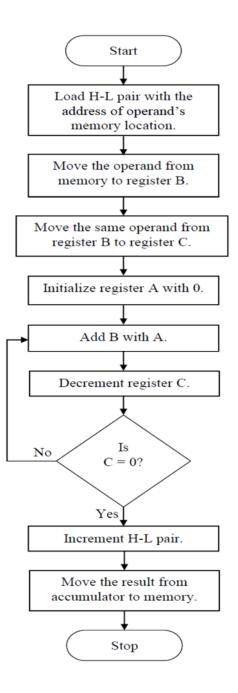

## #) Program- 10

Multiply two 8-bits number. LXI H, 3000H MOV B, M

| INX H      |

|------------|

| MOV C, M   |

| MVI A, OOH |

| ADD B      |

| DCR C      |

| JNZ 200BH  |

| INX H      |

| MOV M, A   |

| HLT        |

|            |

# #) Program -11

Write a program to add two 16 bits number.

| 2000Н      | 15H                                               |

|------------|---------------------------------------------------|

| 2001H      | 10H                                               |

| 2002H      | 25H                                               |

| 2003Н      | 20H                                               |

| Results    | 1015+2025= 303A                                   |

| 2004Н      | 3A                                                |

| 2005Н      | 30                                                |

| LHLD 2000H | : get first 16-bit number in HL                   |

| XCHG       | : save first 16-bits in DE                        |

| LHLD 2002H | : get second 16-bits number.                      |

| MOVA, E    | : get lower byte of first number.                 |

| ADD L      | : add lower byte of second number                 |

| MOV L, A   | : stored the result in L register.                |

| MOV A, D   | : get higher byte of first number.                |

| ADD H      | : add higher byte of second number with no carry. |

| MOV H, A   | : stored result in H register.                    |

| SHLD 2004H | : stored result in memory.                        |

| HLT        | : stop                                            |

|            |                                                   |

## #) program-12

Write a program to find the greatest number.

| Address | Mnemonics | Operand     | Opcode     | Remarks                        |

|---------|-----------|-------------|------------|--------------------------------|

| 2000    | LXI       | Н, 3000Н    | 21         | Load H-L pair with             |

|         |           |             |            | address 3000H.                 |

| 2001    | 00        |             |            | Lower-order of 3000H.          |

| 2002    | 30        | Higher-orde | er of 3000 | )H.                            |

| 2003    | MOV       | А, М        | 7E         | Move the 1st operand from      |

|         |           |             |            | memory to reg. A.              |

| 2004    | INX       | Н           | 23         | Increment H-L pair.            |

| 2005    | MOV       | В, М        | 46         | Move the 2nd operand from      |

|         |           |             |            | memory to reg. B.              |

| 2006    | CMP       | В           | B8         | Compare B with A.              |

| 2007    | JC        | 200BH       | DA         | Jump to address 200BH if there |

|         |           |             |            | is .no carry                   |

| 2008    | 0B        |             |            | Lower-order of 200BH.          |

| 2009    | 20        |             |            | Higher-order of 200BH.         |

| 200A    | MOV       | Α, Β        | 78         | Move smallest from reg.        |

|         |           |             |            | B to reg. A                    |

| 200B    | INX       | Н           | 23         | Increment H-L pair.            |

| 200C    | MOV       | М, А        | 77         | Move the result from reg.      |

|         |           |             |            | A to M                         |

| 200D    | HLT       | 76          | Halt.      |                                |

# Unit: 6

# **Basic I/O, Memory R/W and Interrupt Operations**

## 6.1 Memory Read Operation:

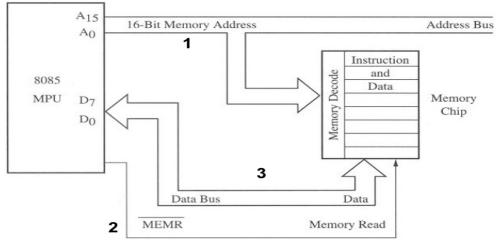

The MPU send a pulse called memory read as the control signal. The pulse activated the memory chip and the content of memory location is place on the data bus and brought inside the microprocessor.

Fig 6.1 Mermory

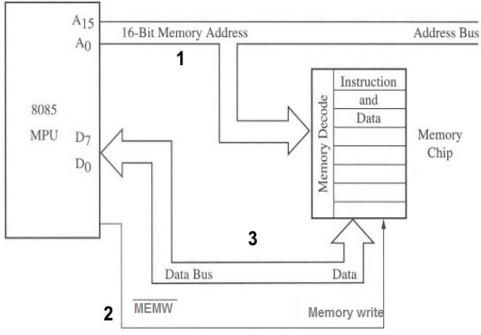

# **Memory Write Operation:**

The MPU send a pulse called memory write as the control signal. The pulse activated the memory chip and the content of memory location is place on the data bus and brought inside the microprocessor.

Fig 6.2: Memory write operation

## 6.2 Direct Memory Access (DMA)

#### What is DMA ?

A technique for transferring data from memory to a device without passing it through the CPU.

## **Application of DMA**

- 1. For making quick backup.

- 2. For real time applications.

- 3. In expansion board such as CD-ROM card are capable to accessing to computer's DMA channel.

## Advantage of DMA

- 1. High data transmission.

- 2. Low power requirement.

- 3. Decrease the CPU load.

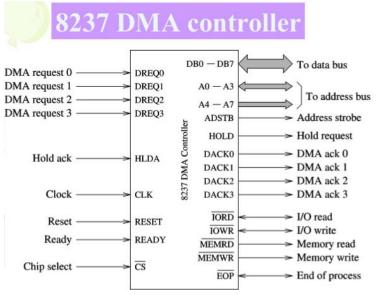

Fig 6.3: 8237 DMA controller

## How DMA techniques work?

## **Basic DMA operation**

- The direct memory access (DMA) technique provides direct access to the memory while the microprocessor is temporarily disabled.

- A DMA controller temporarily borrows the address bus, data bus, and control bus from the microprocessor and transfers the data bytes directly between an I/O port and a series of memory locations.

- The DMA transfer is also used to do high-speed memory-to memory transfers.

- Two control signals are used to request and acknowledge a DMA transfer in the microprocessor-based system.

- The HOLD signal is a bus request signal which asks the microprocessor to release control of the buses after the current bus cycle.

- The HLDA signal is a bus grant signal which indicates that the microprocessor has indeed released control of its buses by placing the buses at their high-impedance states.

- The HOLD input has a higher priority than the INTR or NMI interrupt inputs.

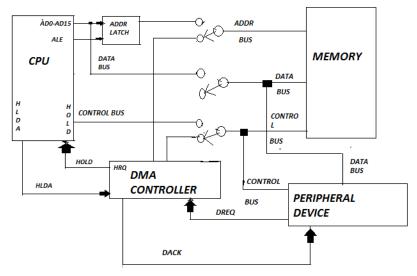

#### DMA Data Transfer scheme

- Data transfer from I/O device to memory or vice-versa is controlled by a DMA controller.

- This scheme is employed when large amount of data is to be transferred.

- The DMA requests the control of buses through the HOLD signal and the MPU acknowledges the request through HLDA signal and releases the control of buses to DMA.

- It's a faster scheme and hence used for high speed printers.

Fig 6.4: DMA Data transfer scheme

## 6.3 Interrrupts

## What is interrupt?

Interrupt is a signal that a peripheral board sends to central processor in order to request attention.

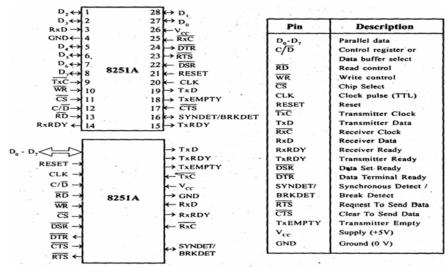

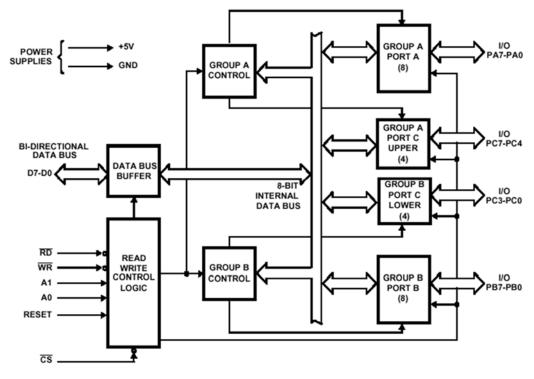

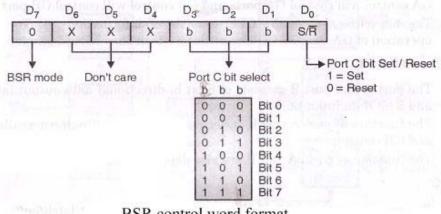

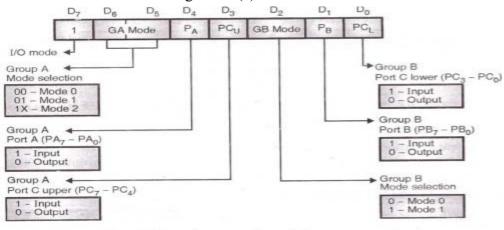

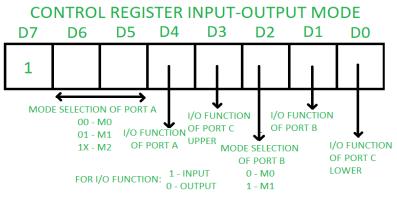

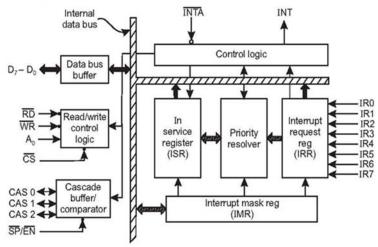

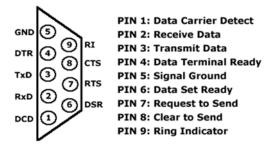

OR,